### **Southern Methodist University**

### **SMU Scholar**

Mechanical Engineering Research Theses and **Dissertations**

**Mechanical Engineering**

Fall 12-19-2020

# Advanced Thermal Characterization and Temperature Control to **Enable the Next Generation of Micro-Electronic Technologies**

Assaad El Helou Southern Methodist University, ahelou@smu.edu

Follow this and additional works at: https://scholar.smu.edu/engineering\_mechanical\_etds

Part of the Mechanical Engineering Commons

#### **Recommended Citation**

El Helou, Assaad, "Advanced Thermal Characterization and Temperature Control to Enable the Next Generation of Micro-Electronic Technologies" (2020). Mechanical Engineering Research Theses and Dissertations. 31.

https://scholar.smu.edu/engineering\_mechanical\_etds/31

This Dissertation is brought to you for free and open access by the Mechanical Engineering at SMU Scholar. It has been accepted for inclusion in Mechanical Engineering Research Theses and Dissertations by an authorized administrator of SMU Scholar. For more information, please visit http://digitalrepository.smu.edu.

# ADVANCED THERMAL CHARACTERIZATION AND TEMPERATURE CONTROL TO ENABLE THE NEXT GENERATION OF MICRO-ELECTRONIC TECHNOLOGIES

|                                            | Approved by: |

|--------------------------------------------|--------------|

|                                            |              |

| Dr. Peter Raad<br>Professor                |              |

| Dr. Ali Beskok<br>Professor                |              |

| Dr. Yildirim Hurmuzlu<br>Professor         |              |

| Dr. David Willis<br>Associate Professor    |              |

| Dr. Archana Venugopal<br>Texas Instruments |              |

# ADVANCED THERMAL CHARACTERIZATION AND TEMPERATURE CONTROL TO ENABLE THE NEXT GENERATION OF MICRO-ELECTRONIC TECHNOLOGIES

A Dissertation Presented to the Graduate Faculty of the

Lyle School of Engineering

Southern Methodist University

in

Partial Fulfillment of the Requirements

for the degree of

Doctor of Philosophy

with a

Major in Mechanical Engineering

by

Assaad El Helou

(M.S., Mechanical Engineering, Southern Methodist University) (B.Eng., Mechanical Engineering, American University of Beirut)

December 19, 2020

Copyright (2020)

Assaad El Helou

All Rights Reserved

#### ACKNOWLEDGMENTS

This work could not have been accomplished without the help and constant support of my advisor, Prof. Peter E. Raad, and the long and engaging research discussions during which I had the chance to benefit from his vast knowledge and experience in the field of thermal sciences and engineering. He had a lasting impact on my career and both my personal and professional character, to which I am grateful. I also would like to acknowledge the faculty of the Departments of Mechanical Engineering and Electrical Engineering at SMU who provided their support in both academics and in research throughout my graduate studies.

I would like to thank TMX Scientific for their support in relation to the thermal imaging system and software and the thermal simulation software, the NSRL cleanroom staff at the UT-Dallas for training and supporting me in microfabrication, and my collaborators at Texas Instruments (TI), the Naval Research Lab (NRL), the Australian National University (ANU), and the Bio-microfluidics Research team at SMU (Dr. Ali Beskok and Dr. Anil Koklu) for their contributions and support. I also gratefully acknowledge Texas Instruments for funding my research endeavors at Nanoscale Electro-Thermal Sciences Laboratory (NETS lab) during my PhD, and the Moody Graduate School for granting me the Dissertation Fellowship Scholarship for my last semester at SMU.

El Helou, Assaad (M.S., Mechanical Engineering, Southern Methodist University) (B.Eng., Mechanical Engineering, American University of Beirut)

Advanced Thermal Characterization and Temperature Control To Enable the Next Generation of Micro-electronic Technologies

Advisor: Dr. Peter Raad

Doctor of Philosophy degree conferred December 19, 2020

Dissertation completed November 6, 2020

In the electronics world, self-heating is an inevitable by-product of electrical activation that has a major impact on device performance and reliability. Thermal technologies have been in constant development to effectively dissipate the generated heat and keep device operation temperatures within reliable limits. Moreover, thermal characterization technologies have been implemented to understand the thermal performance within microelectronic systems, but not without facing experimental and numerical challenges. This work presents advanced thermal investigations, both experimental and numerical, that are adapted and most suited for emerging micro-electronic technologies. Initially, the main experimental and numerical modeling challenges faced in the thermal analysis of micro-electronics are discussed. The advanced thermal characterization techniques are then presented, from high-resolution thermoreflectance based thermal imaging to adaptive multi-grid numerical techniques. Moreover, a coupled experimental and numerical thermal investigation is presented for a more complete thermal assessment of micro-scale semiconductor devices. The coupled approach provides quick and accurate analysis of the thermal aspect of complex micro-electronic device operation and allows the advancement in design and reliability of devices used in numerous applications such as high voltage switching, low power micro-sensing, non-volatile memory, and neuromorphic computing. These thermal characterization strategies are also applied at the integration level of integrated circuits where interconnects reliability is also impacted by their thermal performance. A full review is presented for each of the studied device technologies in an effort to suitably and effectively apply the presented thermal characterization techniques to address the unique requirements and challenges.

# TABLE OF CONTENTS

| LIST | OF    | FIGUR    | ES                                                                  | xii |

|------|-------|----------|---------------------------------------------------------------------|-----|

| LIST | OF    | TABLE    | S                                                                   | xxi |

| СНА  | PTE:  | R        |                                                                     |     |

| 1.   | Intro | oduction | n to Microelectronics Thermal Management                            | 1   |

|      | 1.1.  | Trends   | s in Microelectronic Devices Constrict Thermal Constraints          | 1   |

|      | 1.2.  | Tempe    | erature Effects on Reliability and Performance                      | 3   |

|      |       | 1.2.1.   | Failure and Degradation in High Power Devices                       | 4   |

|      |       | 1.2.2.   | Strict Temperature Control for Micro-Sensing Devices                | 5   |

|      |       | 1.2.3.   | Joule-Heating Induced Electrical Characteristics                    | 5   |

|      | 1.3.  | Outlin   | e                                                                   | 6   |

| 2.   | Exp   | eriment  | al Thermal Characterization                                         | 8   |

|      | 2.1.  | Therm    | nal Microscopy Techniques: Capabilities and Shortcomings            | 9   |

|      |       | 2.1.1.   | Infrared Imaging                                                    | 9   |

|      |       | 2.1.2.   | Micro-TCs and SThM                                                  | 10  |

|      |       | 2.1.3.   | Micro-Raman                                                         | 10  |

|      | 2.2.  | Therm    | noreflectance based Thermal Imaging                                 | 12  |

|      |       | 2.2.1.   | Governing Physics of Reflectance-Temperature Dependence             | 13  |

|      | 2.3.  | TR In    | naging Acquisition Methodology                                      | 15  |

|      |       | 2.3.1.   | TR Experimental Setup for Thermal Microscopy                        | 15  |

|      |       | 2.3.2.   | TR Measurement Procedure                                            | 15  |

|      |       |          | 2.3.2.1. Activation Step for $(\Delta R/R)_a$ Map                   | 18  |

|      |       |          | 2.3.2.2. Calibration Step for $C_{TR}$ Map                          | 18  |

|      |       |          | 2.3.2.3. Extracting Thermal Maps from $C_{TR}$ and $(\Delta R/R)_a$ | 20  |

|    | 2.4. | Challe    | enges and S | Shortcomings of TR imaging                                                                 | 20 |

|----|------|-----------|-------------|--------------------------------------------------------------------------------------------|----|

|    | 2.5. | Therm     | nal Proper  | ty Measurements using TDTR                                                                 | 21 |

| 3. | Nun  | nerical ' | Thermal C   | Characterization                                                                           | 23 |

|    | 3.1. | Full E    | lectro-The  | ermal Modeling                                                                             | 24 |

|    |      | 3.1.1.    | Electrica   | l Modeling Equations for Semiconductor Operation                                           | 24 |

|    |      | 3.1.2.    | Heat Ger    | neration Mechanisms in Microelectronics                                                    | 27 |

|    |      | 3.1.3.    | Tempera     | ture-Dependent Thermal Properties                                                          | 30 |

|    |      | 3.1.4.    | TDTR P      | Property Measurements                                                                      | 32 |

|    | 3.2. |           |             | Iulti-Scale Thermal Modeling for Ultra-fast Computa-<br>ies                                | 35 |

|    | 3.3. | _         |             | Driven Model Optimizations for Full Thermal Charac-                                        | 37 |

| 4. |      |           |             | emoreflectance Imaging Investigation of Self-Heating in on Si, SiC, and Diamond Substrates | 38 |

|    | 4.1. | Introd    | uction      |                                                                                            | 39 |

|    |      | 4.1.1.    | Thermal     | Mapping Challenges for GaN HEMTs                                                           | 40 |

|    |      |           | 4.1.1.1.    | Accessibility                                                                              | 40 |

|    |      |           | 4.1.1.2.    | Accuracy                                                                                   | 41 |

|    |      |           | 4.1.1.3.    | Resolution                                                                                 | 41 |

|    | 4.2. | Metho     | odology     |                                                                                            | 43 |

|    |      | 4.2.1.    | Thermal     | Mapping Procedure                                                                          | 43 |

|    |      |           | 4.2.1.1.    | Thermoreflectance Setup                                                                    | 43 |

|    |      |           | 4.2.1.2.    | Activation                                                                                 | 44 |

|    |      |           | 4.2.1.3.    | Calibration                                                                                | 45 |

|    |      |           | 4.2.1.4.    | Thermal Map                                                                                | 46 |

|    |      | 4.2.2.    | Sample I    | Description                                                                                | 47 |

|    | 43   | Therm     | noreflectan | ce Imaging Results                                                                         | 48 |

|            |      | 4.3.1. | TR Activation                                                                                               | 8 |

|------------|------|--------|-------------------------------------------------------------------------------------------------------------|---|

|            |      | 4.3.2. | TR Calibration                                                                                              | 8 |

|            |      | 4.3.3. | TR Thermal Mapping Results                                                                                  | 0 |

|            |      |        | 4.3.3.1. GaN-on-Si and GaN-Membrane 55                                                                      | 2 |

|            |      |        | 4.3.3.2. GaN-on-SiC and GaN-on-diamond 55                                                                   | 3 |

|            |      |        | 4.3.3.3. Diamond-GaN-on-SiC                                                                                 | 6 |

|            | 4.4. | Conclu | sions                                                                                                       | 7 |

| <b>5</b> . |      |        | l Characterization of AlGaN/GaN HEMTs on Silicon, 4H-Silicon<br>d Diamond Using a Reverse Modeling Approach | 8 |

|            | 5.1. | Introd | action 55                                                                                                   | 9 |

|            |      | 5.1.1. | Thermal Modeling Challenges                                                                                 | 0 |

|            |      |        | 5.1.1.1. Coupled Physics                                                                                    | 0 |

|            |      |        | 5.1.1.2. Uncertain Thermal Properties 60                                                                    | 0 |

|            |      |        | 5.1.1.3. Large Variation in Physical and Time-Scales 6                                                      | 1 |

|            | 5.2. | Metho  | dology                                                                                                      | 2 |

|            |      | 5.2.1. | Coupled Experimental and Numerical Approach                                                                 | 2 |

|            |      |        | 5.2.1.1. Method Description                                                                                 | 2 |

|            |      |        | 5.2.1.2. Outcomes from Optimized Model                                                                      | 3 |

|            |      |        | 5.2.1.3. Selected Parameters for Optimization 65                                                            | 3 |

|            |      | 5.2.2. | Descriptions of Sample Devices                                                                              | 6 |

|            |      | 5.2.3. | Numerical Thermal Modeling                                                                                  | 6 |

|            | 5.3. | Revers | e Modeling Results                                                                                          | 7 |

|            |      | 5.3.1. | GaN-on-Si Optimized Model                                                                                   | 7 |

|            |      | 5.3.2. | GaN-on-SiC Optimized Model                                                                                  | 0 |

|            |      | 5.3.3. | GaN-on-diamond Optimized Model                                                                              | 2 |

|            |      | 5.3.4. | Comparison between Different Substrates                                                                     | 4 |

|    | 5.4. | Conclu | ions                                                                | 6   |

|----|------|--------|---------------------------------------------------------------------|-----|

| 6. |      | _      | Thermal Model for VLSI and ULSI Interconnect Network Reli-          | 1   |

|    |      |        | eation                                                              |     |

|    | 6.1. | Introd | ction 8                                                             | 2   |

|    |      | 6.1.1. | Electromigration Failures and the Degradation of IC BEoL Networks 8 | 2   |

|    | 6.2. | 2D Mo  | lel for Thermal Conductance from an Isolated Interconnect 8         | 6   |

|    |      | 6.2.1. | Reduced Mathematical Models for Effective Conductivity 8            | 7   |

|    |      |        | 6.2.1.1. 1D Model                                                   | 7   |

|    |      |        | 6.2.1.2. Bilotti 2D Model 8                                         | 8   |

|    |      |        | 6.2.1.3. Andrews 2D Model                                           | 8   |

|    | 6.3. | Reduc  | d 3D Thermal Model for an Interconnect Network 8                    | 9   |

|    |      | 6.3.1. | 2+1 D Heat Conduction: The Lossy Wire Model 9                       | 0   |

|    |      |        | 5.3.1.1. The Thermal Entrance Length 9                              | 1   |

|    |      |        | 5.3.1.2. The Maximum Attainable Temperature 9                       | 2   |

|    |      |        | 6.3.1.3. The End Temperatures                                       | 2   |

|    |      | 6.3.2. | Thermal Resistance Network Analysis                                 | 2   |

|    |      |        | 5.3.2.1. ICT Entrance Thermal Resistance                            | 3   |

|    |      |        | 5.3.2.2. Via Thermal Resistance                                     | 3   |

|    |      |        | 6.3.2.3. Cross Configuration Thermal Resistance                     | 5   |

|    |      | 6.3.3. | Iterative Approach to Solve Resistance Network 9                    | 6   |

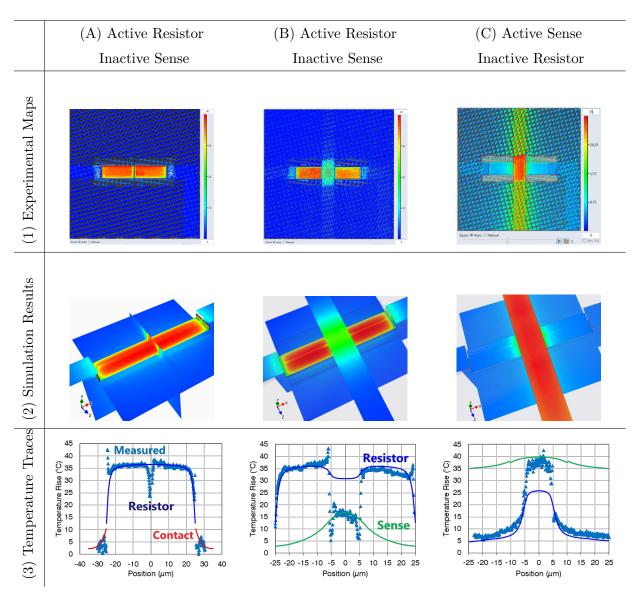

|    |      | 6.3.4. | Model Validation with Simulations and Thermal Imaging 9             | 7   |

|    | 6.4. | TDTR   | Conductivity Measurements of BEoL Thin-film Materials 9             | 8   |

|    |      | 6.4.1. | Studied Materials                                                   | 8   |

|    |      | 6.4.2. | TDTR Results                                                        | 0   |

|    |      | 6.4.3. | TDTR Study Conclusions                                              | 4   |

|    | 6.5  | 2D Co  | phined Model Results                                                | 1/1 |

|    |      | 6.5.1. Validation Simulations with Thermal Maps                                                                        |  |

|----|------|------------------------------------------------------------------------------------------------------------------------|--|

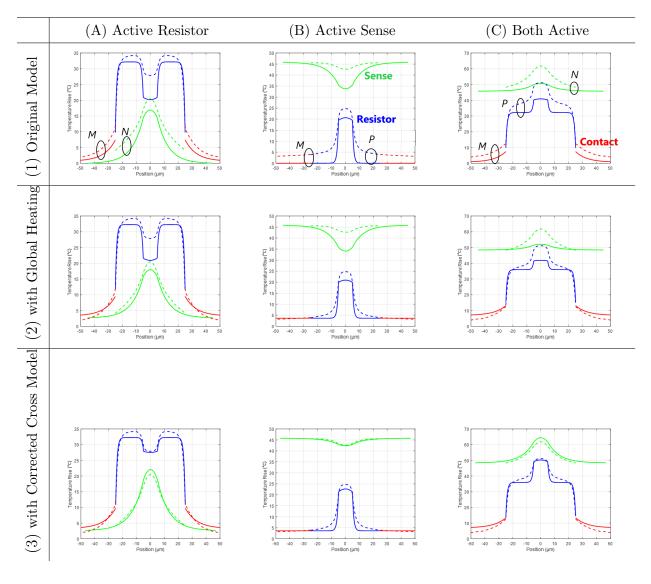

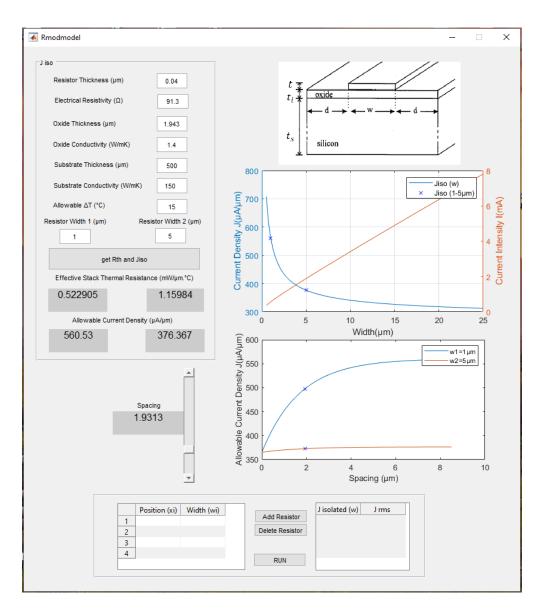

|    |      | 6.5.2. Verifying 2D Reduced model with Simulations                                                                     |  |

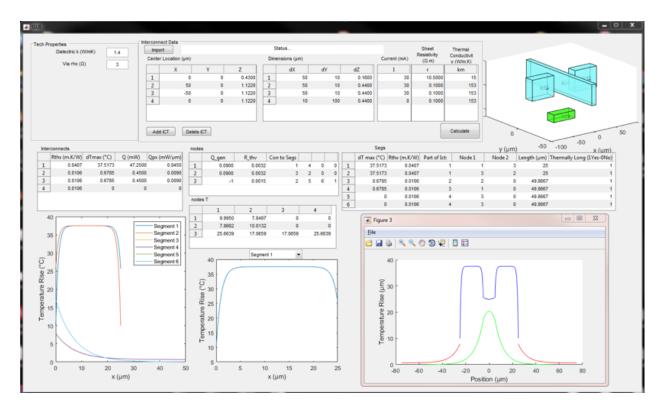

|    | 6.6. | 3D Compact Model Results                                                                                               |  |

|    |      | 6.6.1. Validating Simulations with Thermal Maps                                                                        |  |

|    |      | 6.6.2. Verifying 3D Reduced Model with Simulations                                                                     |  |

|    | 6.7. | Conclusions                                                                                                            |  |

| 7. |      | dardized Heat Spreader Design for Passive Cooling of Interconnects in BEOL of ICs                                      |  |

|    | 7.1. | Introduction                                                                                                           |  |

|    | 7.2. | Thermal Simulation Model                                                                                               |  |

|    | 7.3. | Heat Spreader Design                                                                                                   |  |

|    |      | 7.3.1. Temperature Measurements of Sample Devices                                                                      |  |

|    |      | 7.3.2. Experimentally Validated Thermal Model                                                                          |  |

|    |      | 7.3.3. Simulation and Experimental Results                                                                             |  |

|    |      | 7.3.4. Parametric Study                                                                                                |  |

|    | 7.4. | Conclusions                                                                                                            |  |

| 8. |      | perature Induced Switching in $NbO_x$ Current-Controlled Negative Dif-<br>ntial Resistance (CC-NDR) Memristive Devices |  |

|    | 8.1. | Memristor: the Fourth Fundamental Passive Circuit Element                                                              |  |

|    | 8.2. | Transport phenomena in Thin Oxides                                                                                     |  |

|    | 8.3. | Applications of memristor devices                                                                                      |  |

|    |      | 8.3.1. Non-volatile memory                                                                                             |  |

|    |      | 8.3.2. Neuromorphic computing (neuristor)                                                                              |  |

|    | 8.4. | Temperature-induced CC-NDR switching characteristics                                                                   |  |

|    | 8.5. | Sample Description and Methodology                                                                                     |  |

|    | 8.6  | Electric Field- and Current-Induced Electroforming Modes in NbO., [176] 152                                            |  |

|      | 8.7. | Current Localization and Redistribution as the Basis of Discontinuous Current Controlled Negative Differential Resistance in $NbO_x$ [177] | 54         |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | 8.8. | Schottky barrier induced asymmetry in the negative differential resistance response of $Nb/NbO_x/Pt$ cross-point devices [178]             | 61         |

|      | 8.9. | Thermal Conductivity of Amorphous Sub-stoichiometric ${\rm NbO}_x$ for Memristors Applications using Transient-Domain Thermoreflectance    | 64         |

|      |      | 8.9.1. Experimental Methods                                                                                                                | 66         |

|      |      | 8.9.2. TDTR Results and Discussion                                                                                                         | 66         |

| 9.   |      | racterization of Temperature Rise in AC Electro-thermal Flow Using rmoreflectance Method [129]                                             | 69         |

|      | 9.1. | AC Electrothermal Flow for Electrokinetic Actuation of Liquid Media 1                                                                      | 70         |

|      | 9.2. | Temperature Control for ACET Applications                                                                                                  | 71         |

|      | 9.3. | Materials and Methodology                                                                                                                  | <b>7</b> 3 |

|      | 9.4. | Results                                                                                                                                    | 77         |

|      |      | 9.4.1. Frequency-Dependent Self-Heating                                                                                                    | 77         |

|      |      | 9.4.2. Voltage-Dependent Self-Heating                                                                                                      | <b>7</b> 9 |

|      |      | 9.4.3. Power-Loss Dependent Self-Heating                                                                                                   | 81         |

|      | 9.5. | Conclusions                                                                                                                                | 84         |

| 10.  | Con  | clusions                                                                                                                                   | 85         |

| DIDI | IOC  | PAPHY 1                                                                                                                                    | Q.7        |

## LIST OF FIGURES

| 'age | .e                                                                                                                                                                                                                                                                                                                                                        | Figure |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

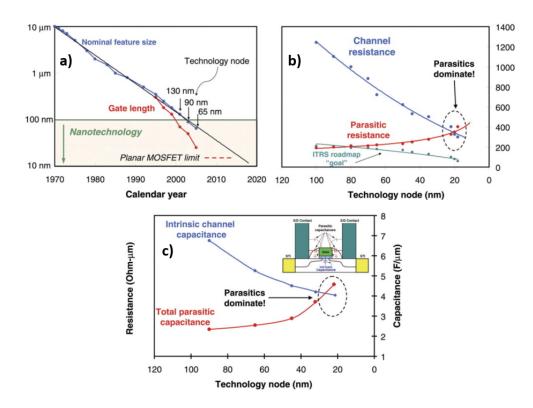

| 2    | a) Logic technology node and gate length b) resistance and c) capacitance of different technologies showing the improvement in performance with device scaling. (Adapted from [248])                                                                                                                                                                      | 1.1    |

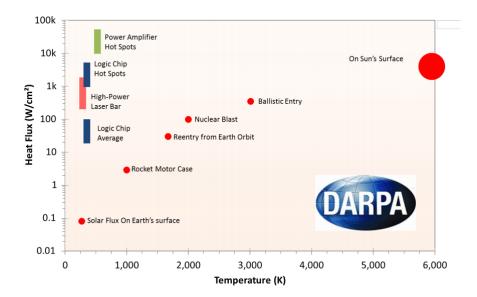

| 3    | Graph showing the increased heat flux densities in advance microelectronic devices (represented by bars) resulting from increasing power levels and downscaling in device sizes. Red circles show comparison to other natural and man-made heat generation rates for scale. (Source: DARPA)                                                               | 1.2    |

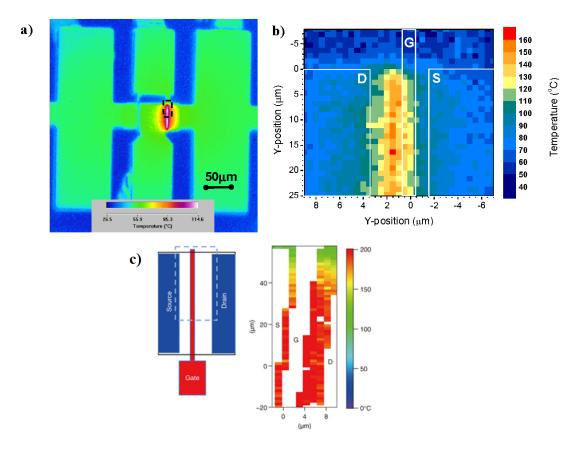

| 11   | Thermal maps of active GaN HEMT using a) IR and b) micro-Raman imaging from Sarua et al. [220]. c) Device measurement region and Raman measurements adapted from Hiroki et al. [105]. The high-resolution requirements are evident especially as device dimensions near the submicron scale.                                                              | 2.1    |

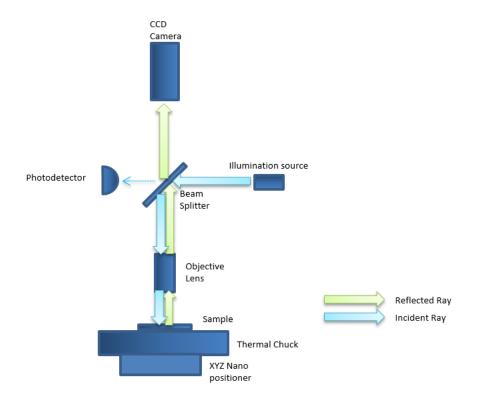

| 16   | Schematic showing optical setup of TR imaging imaging system and the incident and reflected light path from the sample.                                                                                                                                                                                                                                   | 2.2    |

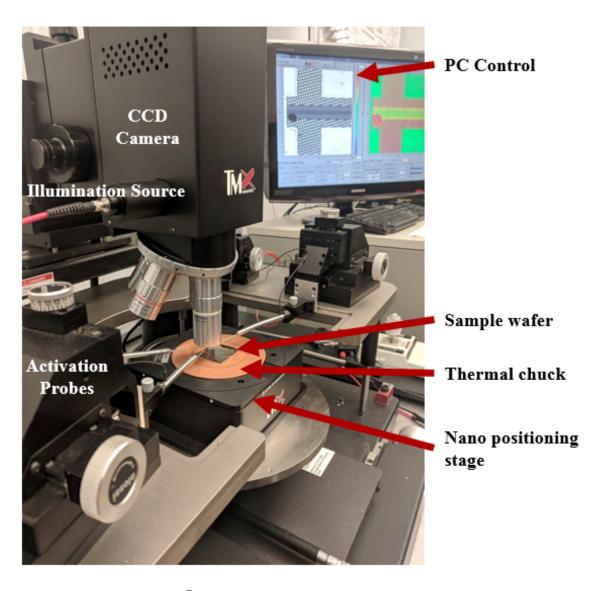

| 17   | TMX T°Imager® setup showing activation, temperature, PC, nano-positioning, and light control used for sample thermal imaging                                                                                                                                                                                                                              | 2.3    |

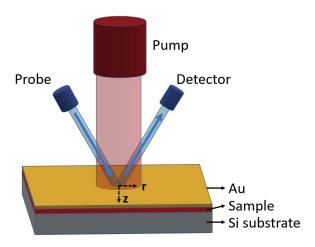

| 22   | Schematic representation of pump-and-probe technique for the time-domain thermoreflectance.                                                                                                                                                                                                                                                               | 2.4    |

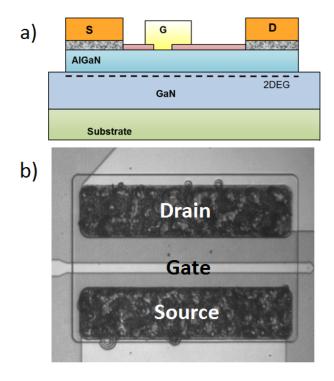

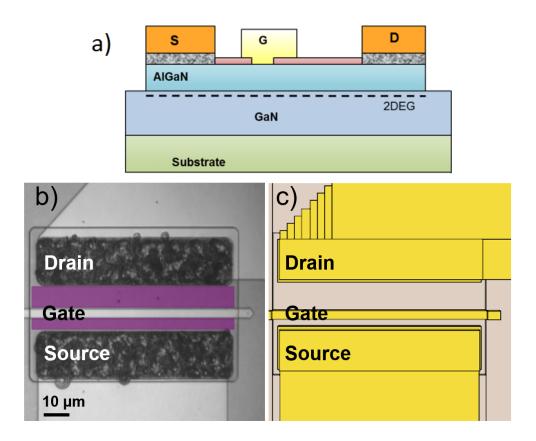

| 43   | a) Schematic of HEMT device structure. The substrate is either Si, SiC, Diamond, or is etched b) Top view image showing Source, Drain and Gate contacts.                                                                                                                                                                                                  | 4.1    |

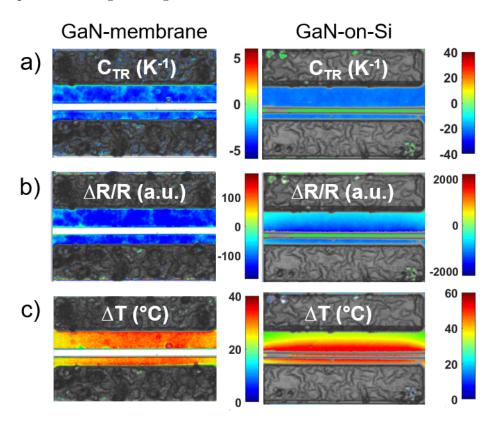

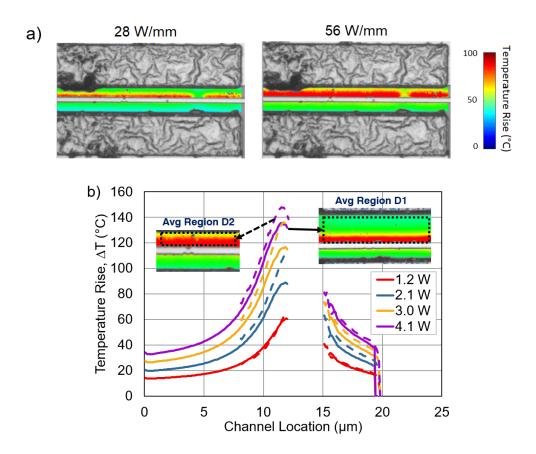

| 44   | Sample a) calibration map for $C_{TR}$ showing a global reflectance change response from the GaN material, b) reflectance change map $\Delta R/R$ showing the localized response within the GaN Channel Region, c) the resulting temperature rise map $\Delta T$ for the active GaN-membrane and GaN-on-Si device showing self-heating within the channel | 4.2    |

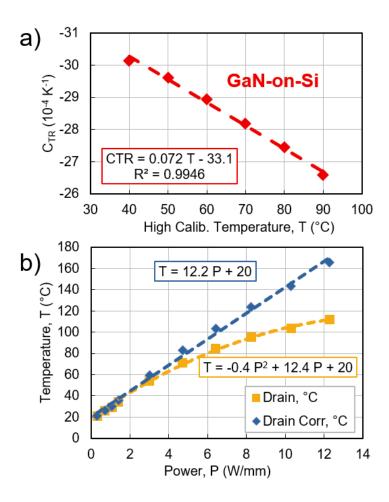

| 49   | a) The calibration curve of CTR vs T showing a decrease in TR response at higher temperatures. b) Temperature rise curve as a function of applied power for GaN-on-Si device before and after correction for CTR-T dependence. The correction recovers the linearity of P-T relation for the GaN-on-Si devices.                                           | 4.3    |

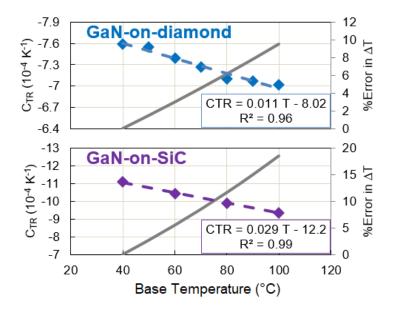

| 4.4 | Calibration results for GaN-on-SiC and GaN-on-diamond showing $C_{TR}$ linear decrease with temperature                                                                                                                                                                                                                                                                                                                                            | 50         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

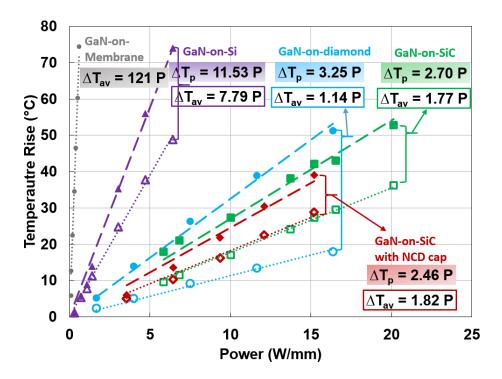

| 4.5 | A summary of the measured Average (open markers) and Peak (solid markers) experimental temperature rise (in °C) within the active channel of the measured GaN HEMT devices on the different substrates. The linear experimental fit are shown for the measurement data for the average (in dotted lines) and peak temperature (in long dashed lines). The heating rate (total thermal resistance) is reported from the linear regression analysis. | 51         |

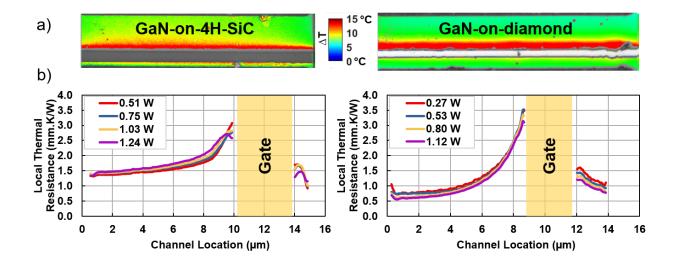

| 4.6 | <ul> <li>a) Measured thermal maps showing temperature rise in GaN HEMTs active region on SiC (left) and diamond (right) substrate (P≈0.5 W, 6.6 W/mm).</li> <li>(b) The local thermal resistance across the Gate-Drain channel shows peak temperature rise at the drain-side edge of the gate</li></ul>                                                                                                                                            | 54         |

| 4.7 | a) Measured thermal maps for GaN-on-diamond device 2 [239] with a different gate geometry than our measured device b) Comparison of temperature profile for both measured GaN-on-diamond devices with different drain channel length shows similar temperature rise                                                                                                                                                                                | 55         |

| 5.1 | a) Schematic of HEMT device structure. The substrate is either Si, SiC, Diamond, or is etched b) intensity image (1024x1024 pixels) of the device under 100× magnification showing the Source, Drain and Gate contacts. Purple regions indicate the GaN drain and source channel where the thermal measurements are conducted c) device model built to scale in T°Solver®.                                                                         | 64         |

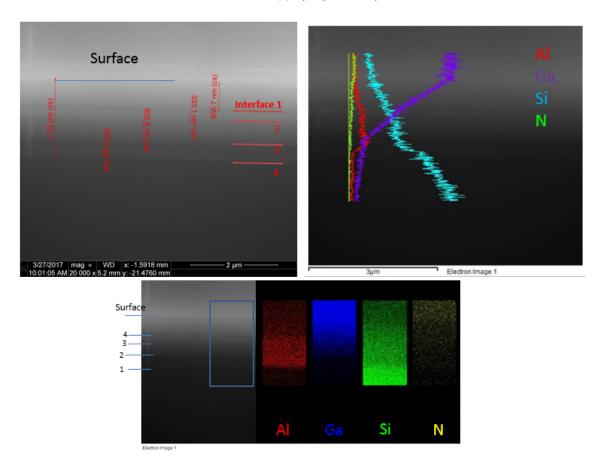

| 5.2 | x-SEM measurements showing thickness and composition of GaN/AlGaN stack.                                                                                                                                                                                                                                                                                                                                                                           | 65         |

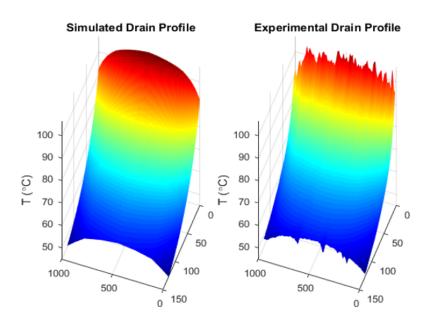

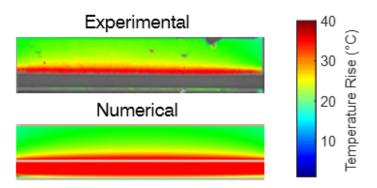

| 5.3 | Converged temperature profiles for the matched numerical and experimental thermal maps for the gate-drain access region of a GaN-on-Si device for a DC power level $(I_{DS} \times V_{DS})$ of 6.4 W/mm                                                                                                                                                                                                                                            | 69         |

| 5.4 | Comparison of matched experimental and simulation results for GaN-on-SiC for an activation power level of 15.7 W/mm                                                                                                                                                                                                                                                                                                                                | <b>7</b> 0 |

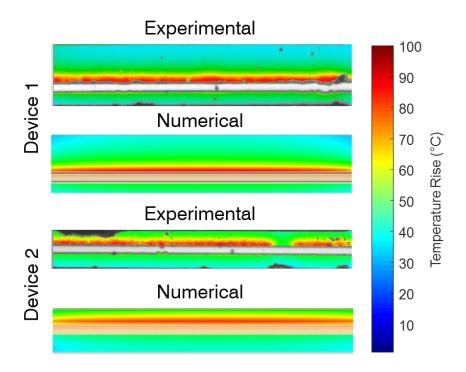

| 5.5 | Sample temperature rise profile for the matched numerical and experimental results for GaN-on-diamond device 1 and device 2                                                                                                                                                                                                                                                                                                                        | <b>7</b> 3 |

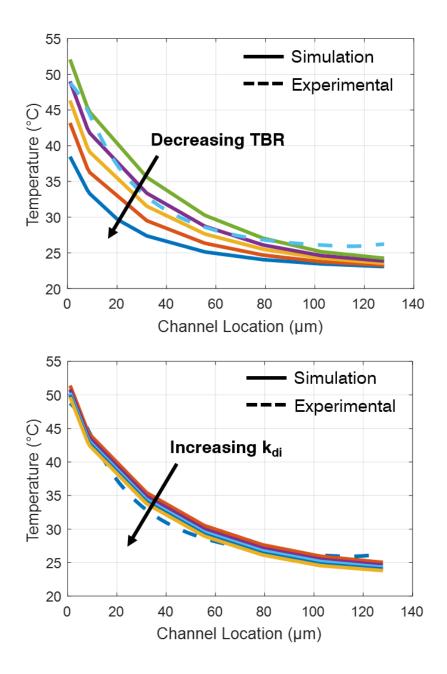

| 5.6 | Variation of temperature profile in GaN-on-Diamond HEMT for (a) the TBR range between 25 and 5 m <sup>2</sup> K/GW and (b) for the conductivity range $k_{di,xz}$ between 1000 and 1400 W/m.K with $k_{di,y}$ =1.45× $k_{xz,di}$                                                                                                                                                                                                                   | 77         |

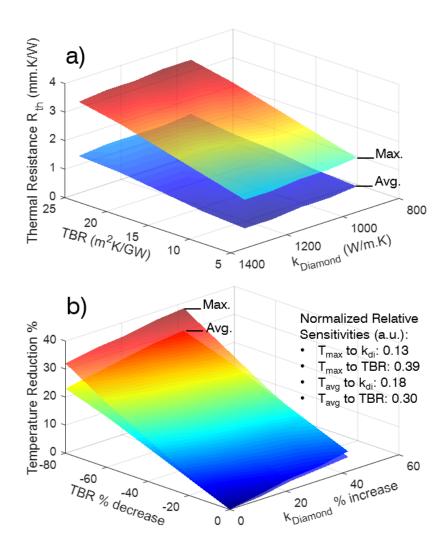

| 5.7 | a) Results of parametric study showing the total thermal resistance for the studies values of diamond conductivities and TBR values, based on maximum and average GaN channel temperatures, and power level of 16.4 W/mm. The through-plane conductivity is taken as $1.45 \times k_{xz,di}$ . b) The corresponding percent change in self-heating temperature rise with reported sensitivity values to changes in $k_{di}$ and TBR                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

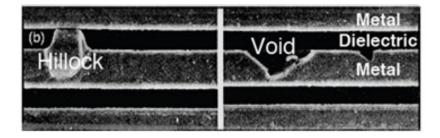

| 6.1 | Image of interconnect showing hillock and void formation due to material transport under Electromigration. (Source: Kyung-Hoae 2011)                                                                                                                                                                                                                                                                                                                                                 |

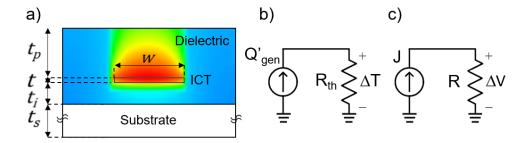

| 6.2 | a) Schematic of the device structure considered for the 2D thermal model showing the ICT embedded in the dielectric medium b) Corresponding thermal resistive circuit showing the heat source generated $Q'_{gen}$ and the total thermal resistance $R_{th}$ c) The electrical activation circuit for the ICT showing the electrical resistance $R$ and current density $J$                                                                                                          |

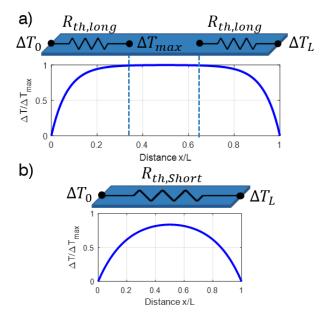

| 6.3 | Schematic showing a) thermally long $(L/\lambda_h > 5)$ and b) thermally short $(L/\lambda_h < 5)$ ICT with the considered entrance thermal resistance at the nodes and the associated temperature distribution for a given $\lambda_H$ . Zero boundary condition is considered $\Delta T_n = \Delta T_0 = 0$ and $\Delta T_k = \Delta T_L = 0$ at both ends $x = 0$ and $x = L$ . Note that the temperature distribution in a thermally short ICT does not reach $\Delta T_{max}$ . |

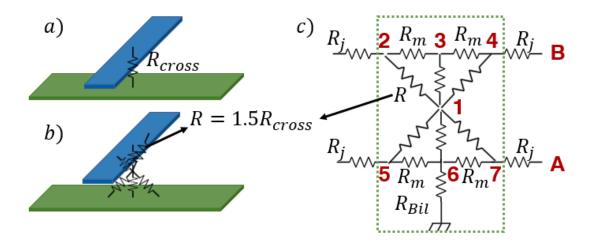

| 6.4 | Schematic showing the resistive network configuration for a) Single Resistive Cross model b) Six Resistors Cross Model based on [40]. The value of R is such that the equivalent network resistance is equal for the two ICTs in both configurations. c) Resistance network schematic showing the six-resistor model [48] connected to the ICT segment ends                                                                                                                          |

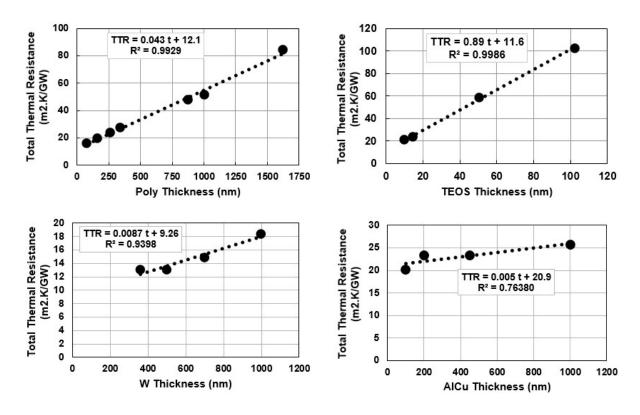

| 6.5 | Total thermal resistances obtained for the thin-film samples as function of film thickness. The slope and intercept of each data fit are used to extract the intrinsic thermal conductivity of the film and its interface thermal resistance.                                                                                                                                                                                                                                        |

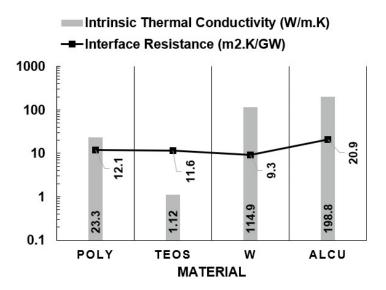

| 6.6 | Summary of the measured intrinsic thermal conductivities of the BEoL materials and their interface thermal resistances                                                                                                                                                                                                                                                                                                                                                               |

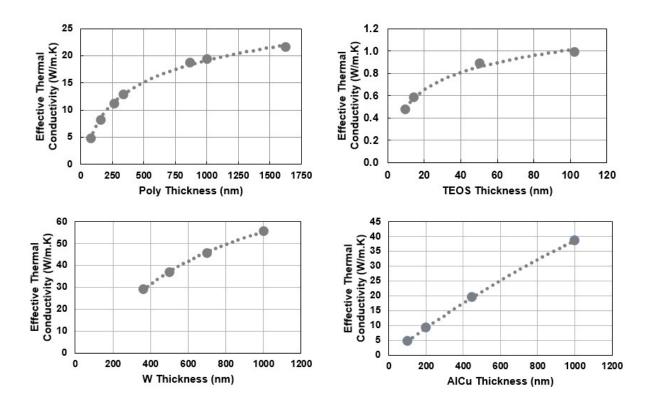

| 6.7 | The calculated effective thermal conductivities of the sample films as reconstructed from the extracted intrinsic thermal conductivities and interface resistances                                                                                                                                                                                                                                                                                                                   |

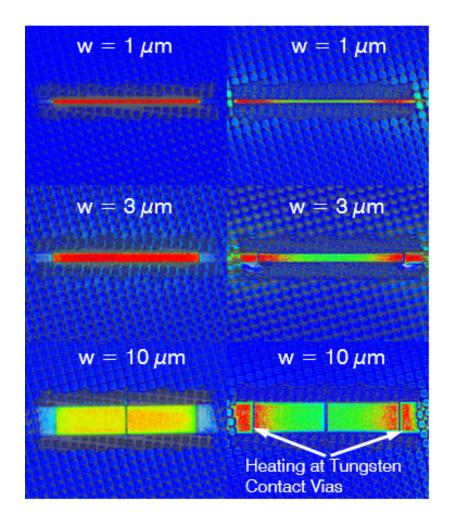

| 6.8 | Thermal maps of the sample BEoL devices micro-resistors of widths 1, 3 and 10 $\mu$ m at the different locations: Level 1 of Polysilicon (Poly) shown in the left column and level 2 of AlCu metalization (MET1) shown in the right column                                                                                                                                                                                                                                           |

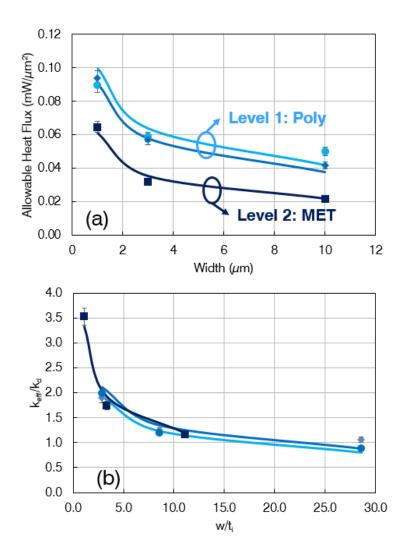

| 6.9  | Comparison of the heating rate for measured ICT samples as compared with their estimates from the reduced model, with $\kappa_d = 1.1W/m.K$                                                                                                                                                                                                                                                                                                                                              | 107 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

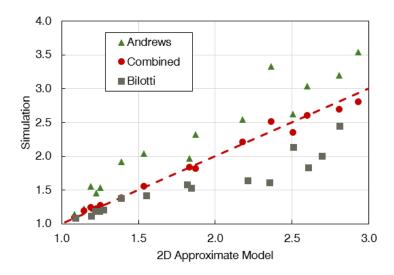

| 6.10 | Comparison between the newly developed combined model and the simulation results, the models of Bilotti and Andrews are also shown for each case to highlight the improvement of using the combined model                                                                                                                                                                                                                                                                                | 110 |

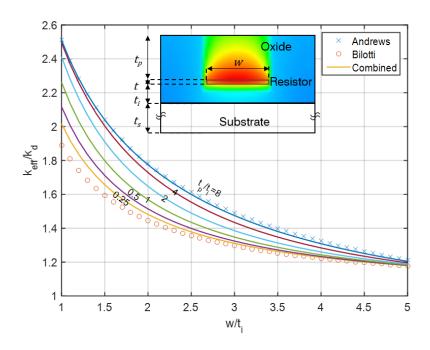

| 6.11 | Combined model chart showing effective conductance $\kappa_{d,eff}/\kappa_d$ from an ICT of width $w$ , insulation thickness $t_i$ and passivation thickness $t_p$ , all of which are denoted in the added schematic. The Bilotti and Andrews cases show the extreme effects of, respectively, ignoring passivation or making it infinite.                                                                                                                                               | 111 |

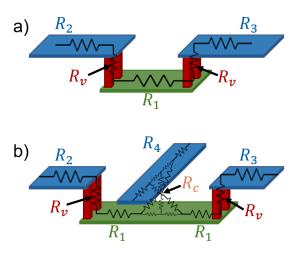

| 6.12 | Schematic showing the resistive network configuration for a) an polyresistor ICT in Level 1 between two via connections to contact leads in the higher MET level, and b) the same configuration with a "sense" lead in the MET layer with the cross coupling. The resistive network that connects the device components is also shown in an overlay that shows the thermal resistance coupling of the different features (entry, via, and cross resistance).                             | 112 |

| 6.13 | Graphical user interface for 2D reduced model built in MATLAB GUIDE.  The interface shows input electrical and thermal parameters for an isolated interconnect, and provides the allowable current density levels.  The model also reports on the effective thermal conductivity of the surrounding dielectric.                                                                                                                                                                          | 119 |

| 6.14 | Graphical user interface for the 3D reduced model built in MATLAB GUIDE. The interface shows input electrical and thermal parameters for an isolated interconnect as well as the dimensions of the interconnect and its location within the BEoL stack. The model provides the allowable current density levels as well a temperature distribution along the length of each interconnect segment. The insert graph shows the overlaid temperature of the test samples used in this study | 120 |

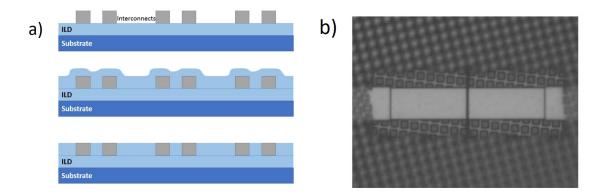

| 7.1  | a) Schematic showing stages of CMP fill fabrication process with a newly deposited MET layer (top) a deposited dielectric layer for interconnect passivation (middle) and after CMP process provides a level surface for deposition of next layer (bottom). b) Snapshot of BEoL sample device showing microresistor element and contact leads surrounded by the square CMP fill patterns. An exclusion zone around the device is used for optical access to the device.                  | 123 |

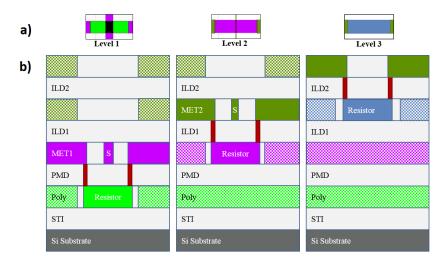

| 7.2 | a) Device illustrations as seen from the top view. b) Schematic of the three-level BEOL stack showing the resistors devices with the contact and sensing leads (solid color), and the CMP fill regions (hatched color) at the three MET levels: Level 1 Poly (Left), Level 2 AlCu (Middle), Level 3 AlCu (Right)                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

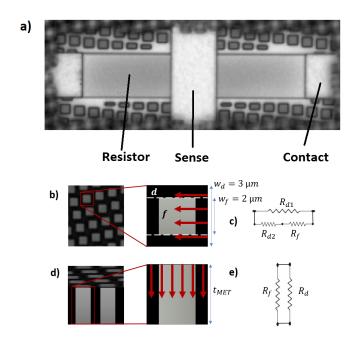

| 7.3 | a) Top view intensity map of a sample device under test (DUT). The center resistor is at level 1 and surrounded by the CMP fill square pattern. Two contact leads are seen at both resistor ends a central sensing lead is running transversely above the resistor. More CMP fill is also seen at the higher levels of the BEOL stack; b) Top view showing fill pattern unit cell dimensions and in-plane heat transfer path. c) Equivalent thermal resistance circuit model for calculating in-plane effective thermal conductivity. d) Side view of CMP fill pattern unit cell and heat conduction path e) Equivalent thermal resistance circuit model for through-plane thermal conduction. density $w_f^2/w_d^2$ |

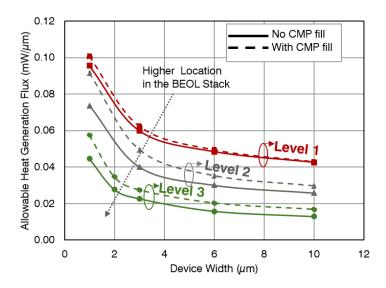

| 7.4 | Simulation results of heat generation limit for an allowable temperature rise $(\Delta T)$ of 15 °C for interconnects at the three MET levels as function of device (resistor) width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

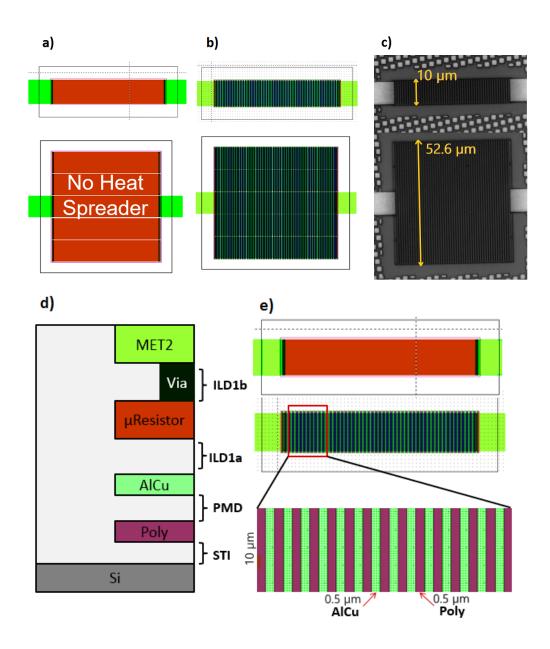

| 7.5 | Schematics showing the design configurations of the microresistor BEOL devices: $a$ ) without the heat spreader and $b$ ) with the heat spreader. $c$ ) The actual device under test intensity image as obtained by the camera. The top row shows the narrow HS configuration while lower part shows the wide HS configuration. $d$ ) Side view showing the schematic of the HS features at the different levels of the BEOL $e$ ) Top view showing the staggered array structure of the Poly and AlCu lines beneath the resistor 131                                                                                                                                                                                |

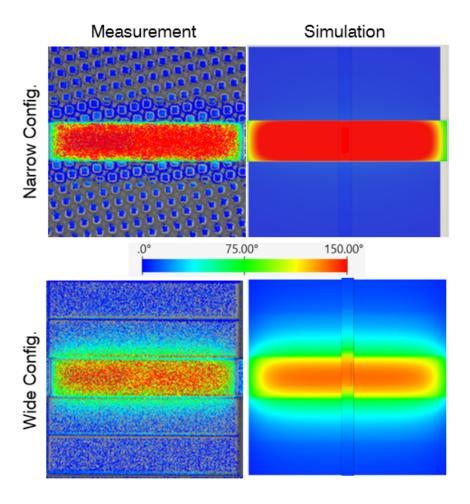

| 7.6 | Thermal simulations of activated devices (Right) compared to experimental temperature maps (Left) of device with narrow heat sink (Top) and wide heat sink (Bottom) for a heating rate of 1.54 $mW/\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

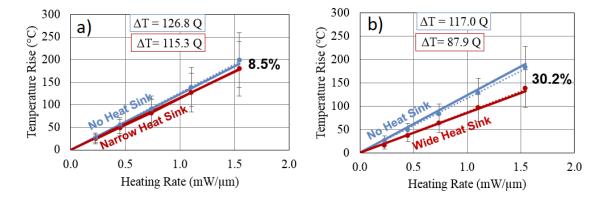

| 7.7 | Temperature rise profile showing cooling effect and the reduction in overall thermal resistance experienced by the 10 $\mu m$ interconnect in Level 3 for device with a) narrow HS and b) with wide HS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

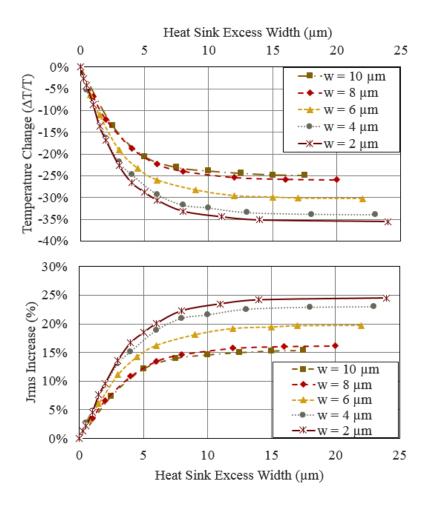

| 7.8 | Cooling effectiveness of different widths of HS for different micro-resistor widths (Top) and the associated percent increase in current density $J_{RMS}$ allowance (Bottom).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

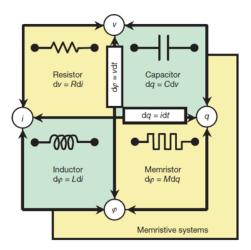

| 8.1 | The four fundamental passive circuit devices relating the four electrical parameters $(i, v, \phi, \text{ and } q)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

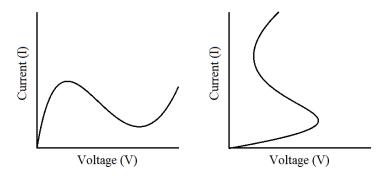

| 8.2 | IV characteristics showing N-type and S-type Negative Differential Resistance (NDR) behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

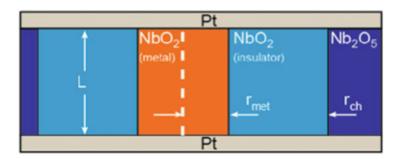

| 8.3  | Metallic filament forms at temperature exceeding the metal-insulator-transition (MIT) temperature ( $\approx 1000 \text{ K}$ ) [196]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

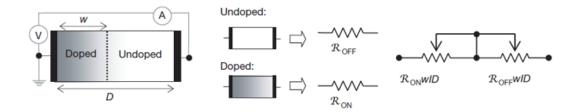

| 8.4  | Schematic showing the resistive memory behavior (re-RAM) of transition-metal oxides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

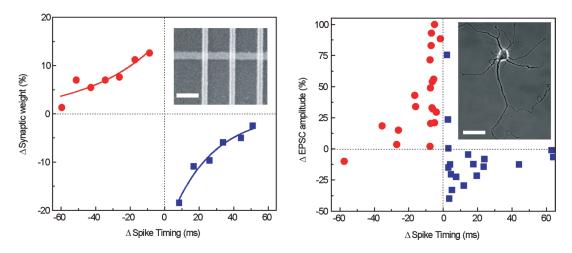

| 8.5  | Activation synaptic behavior in memristors as compared to an actual neuron [118].145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.6  | Biologically inspired neural networks based on the functioning of the synapse [118]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

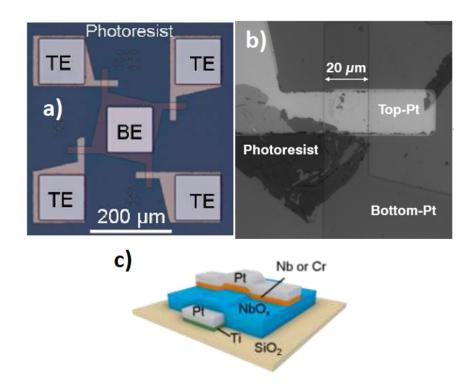

| 8.7  | Transmission electron microscopy images showing the metallic phase formed after device switching [140]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

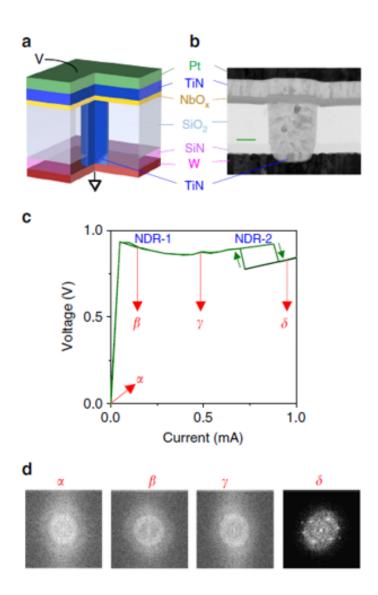

| 8.8  | a) Device structure as seen under $20\times$ magnification showing the four patterned top and bottom electrodes (TE and BE) and the resulting four cross-point devices. b) Intensity map of crosspoint device under $100\times$ as seen with the camera under monochromatic illumination. c) Schematic of the crosspoint devices showing the Pt electrodes and the NbO <sub>x</sub> thin-film. 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

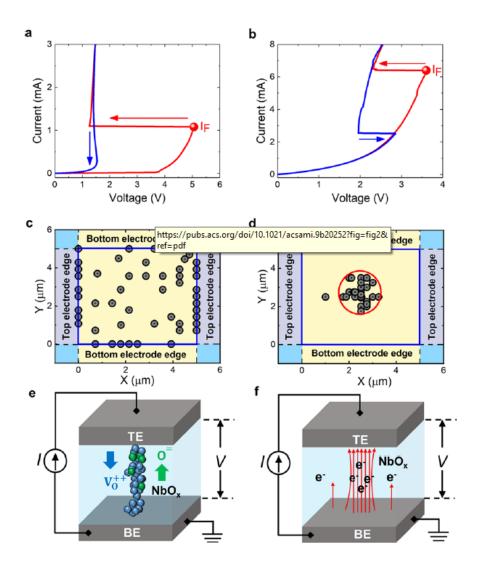

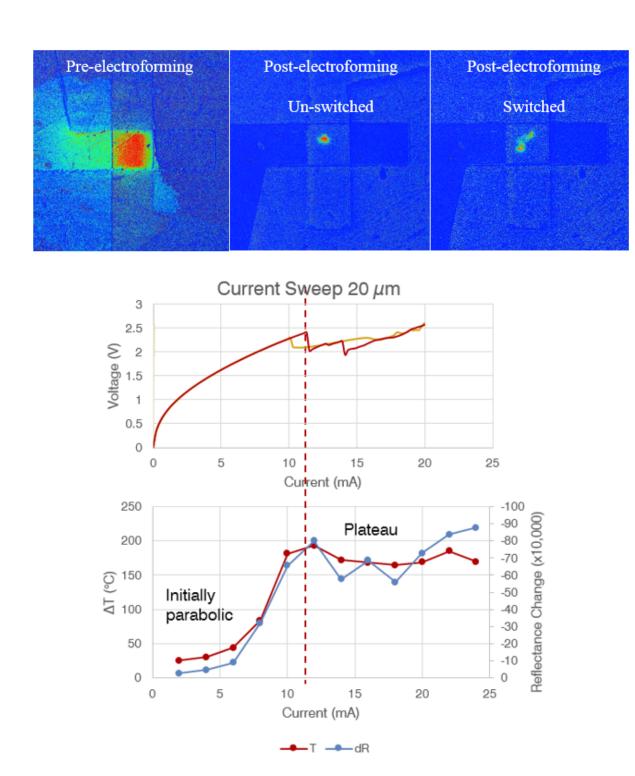

| 8.9  | Electroforming and filament distributions: (a) electroforming characteristics of a 5 $\mu$ m Pt/Nb/NbO2.6/Pt device, (b) electroforming characteristics of a 5 $\mu$ m Pt/Nb/NbO1.92/Pt device, (c) schematic representation of filament distribution in a 5 $\mu$ m × 5 $\mu$ m cross-point device with low-conductivity NbO <sub>x</sub> (x = 2.60) films, (d) schematic representation of filament distribution in a 5 $\mu$ m × 5 $\mu$ m cross-point device with high-conductivity NbO <sub>x</sub> (x = 1.92) films, (e) schematic of an oxygen vacancy filament formed by the field-induced generation, drift, and diffusion of oxygen vacancies, and (f) schematic of a transient current filament due to current bifurcation. Note that each dot in (c, d) represents a single device and the filament distributions represent 75 separate measurements for each film [176]. |

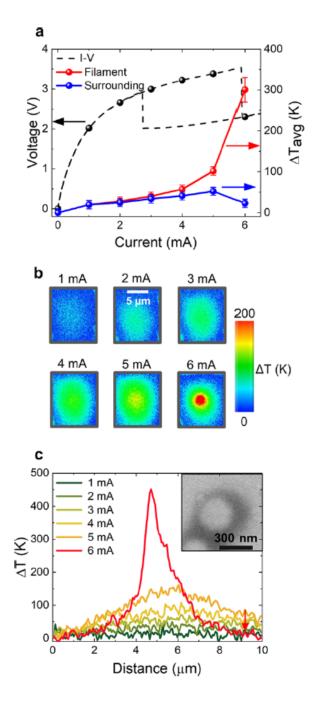

| 8.10 | In situ thermoreflectance measurements: a) in situ (points) and ex situ (line) current-voltage characteristics of a 10 $\mu$ m $\times$ 10 $\mu$ cross-point device with a high conductivity NbO <sub>x</sub> (x=1.92) film, and the temperature of the filamentary and surrounding regions of the film (shown by circles in panel b), b) Two-dimensional temperature maps of the top electrode surface for different device currents. The inset shwos a back-scattered electron image of the filamentary region in the oxide film (i.e, after removing top electrode).                                                                                                                                                                                                                                                                                                               |

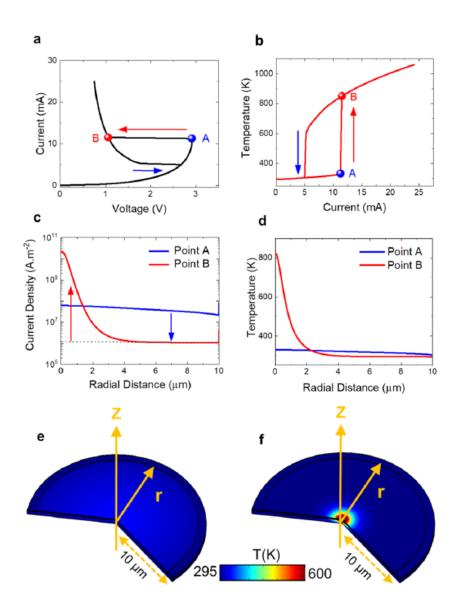

| 8.11 | Finite element simulatio: a) current-voltage characteristics during bidirectional current sweep, b) maximum temperature in oxide film as a function of device current, c) current density distribution before and after bifurcation, d) temperature distribution before and after bifurcation, e) before (point A) and f) after current bifurcation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

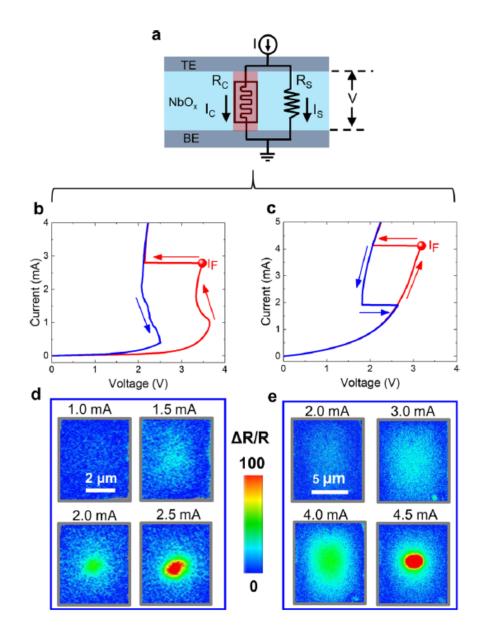

| 8.12 | Core-Shell model and current bifurcation: a) schematic of the CS model of a negative differential resistance device, b) electroforming characteristics of a $5\mu m \times 5\mu m$ device with NbO <sub>x</sub> (x-2.22 film), c) electroforming characteristics of a $10\mu m \times 10\mu m$ device with NbO <sub>x</sub> (x-2.22 film), d) in situ thermoreflectance maps of $5\mu m \times 5\mu m$ device during electroforming e) in situ thermoreflectance maps of $10\mu m \times 10\mu m$ device during electroforming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

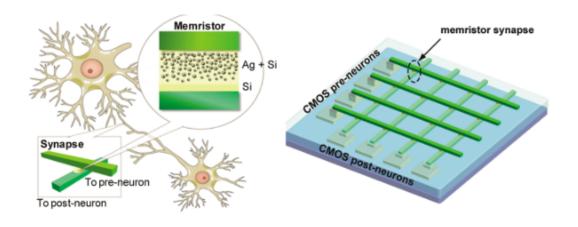

| 8.13 | Structure of the studied NDR crosspoint device showing snapback switching and saturation of filamentary conduction after current bifurcation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

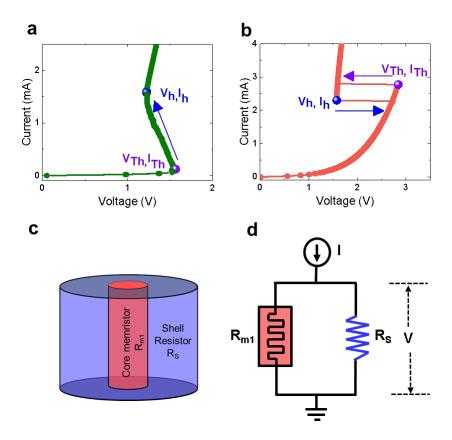

| 8.14 | I-V characteristics showing a) S-type NDR behavior and b) snapback (SB) NDR behavior. c) model of conductive paths in transition metal oxide $(NbO_x)$ layer showing core and shell with representative electrical resistance. d) representative electrical circuit with constant current source, and the respective resistance of shell and variable resistance (memristor) of core [177]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

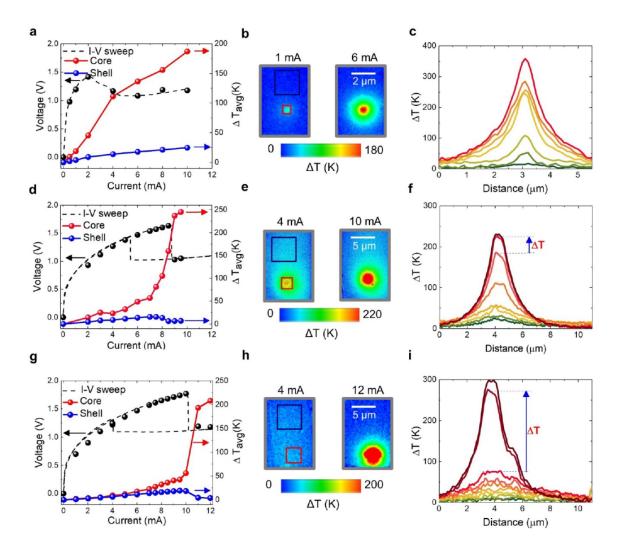

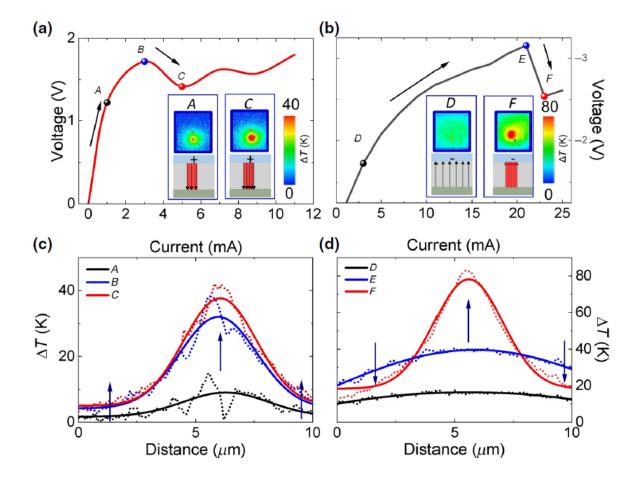

| 8.15 | In-situ temperature measurements of S-type and snap-back NDR. a) Current-voltage (I-V) characteristics and average temperature rise of the filament and surrounding area (the area used for averaging is indicated by boxes in b) as a function of applied current, b) 2D maps of the surface temperature rise in a 5 $\mu$ m device operating at 1 mA and 6 mA, c) Temperature (current) localization of S-type NDR in the post-formed device at different current levels as shown in a, d) I-V characteristics and average temperature rise of the permanent filament and surrounding area (indicated by boxes in e) as a function of applied current, e) 2D map of the surface temperature rise in a 10 $\mu$ m device at pre-threshold (4mA) and post-threshold (10 mA) currents, f) Temperature (current) localization in a post-formed device at different currents as shown in d (the blue arrow indicates snap-back transition), g) I-V characteristics and average temperature rise of the current filament and surrounding area (indicated by boxes in h) as a function of applied current, h) 2D map of the surface temperature in a 10 $\mu$ m device at pre-threshold (4 mA) and post-threshold (12 mA) currents, i) Temperature (current) localization due to current bifurcation in the device without permanent filament as shown in g (the blue arrow indicates snap-back transition) [177]. 162 |

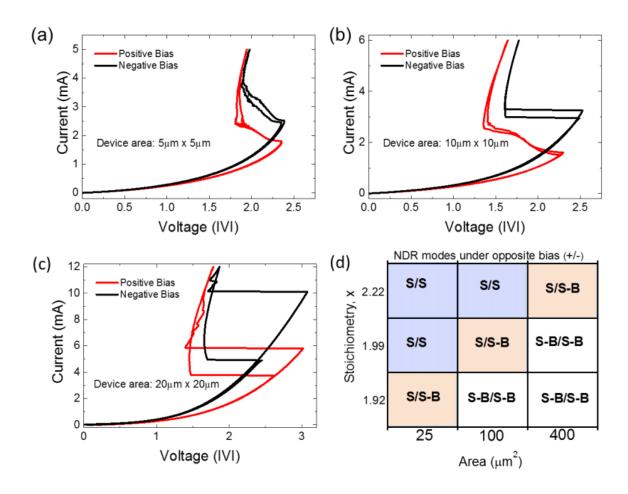

| 8.16 | (a-c) Asymmetric NDRs observed in Nb/NbO <sub>x 1.99</sub> /Pt MOM under positive and negative polarity. (d) Matrix representation of dependencies of NDR on stoichiometry and device area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.17 | a), b) In situ I -V characteristics of a 10×10 μm² Au (75 nm)/Nb(5 nm)/NbO1.99 (approximately 45 nm)/Pt (25 nm) device showing S-type NDR under positive bias and snapback under negative bias, respectively. Insets show the in situ thermoreflectance (ΔR/R) maps of the 10×10 μm² device during corresponding bias polarity. c) Temperature profile through the filamentary region for different points in the current-voltage curve during positive bias. d) Temperature profile of the same device for different points in the current-voltage curve during negative bias. Note: the temperature map and the I-V characteristics shown in Figure 3 are also obtained for 5×5 μm² devices with lower threshold currents, and a snapback response observed under negative polarity and S-type NDR under positive polarity. But in this case, the filament is observed to form around the edges due to the dominance of edge effect in smaller area cross-point devices with a thick (75-nm Au in this case) capping layer [25]. The short-dashed curves in c) and d) represent the experimental data and the smooth lines show Gaussian fits of the corresponding experimental data. A, B, and C denote sub-threshold, threshold, and post-threshold points respectively in the I -V characteristic obtained under positive bias, while D, E, and F denote the same for negative bias polarity [178]. |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

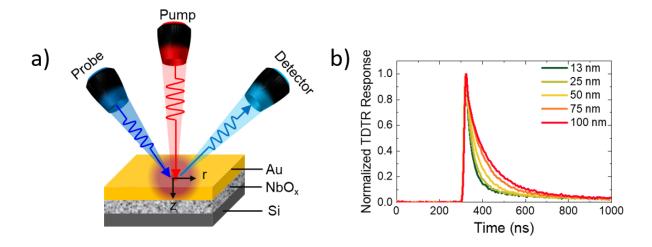

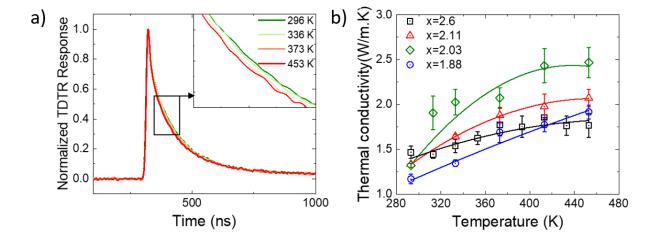

| 8.18 | a) Schematic representing the Pump-and-Probe setup used to conduct transient-domain thermoreflectance conductivity measurements. b) TDTR normalized response showing the heating and temperature decay profile as measured at the gold surface of the blanket film samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.19 | a) The TDTR response is presented as a function of temperature for the thickest (100 nm) sample. b) Thermal conductivity as a function of temperature for different stoichiometric NbOx films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

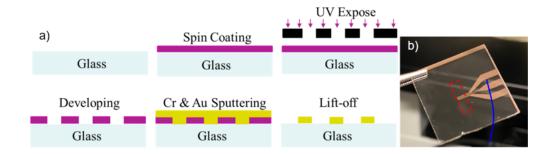

| 9.1  | a) Process flow of electrode fabrication using photolithography technique and b) image of intedigitated electrodes fabricated on glass substrate.  The micro-fluidic channel is indicated with red dashed rectangle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

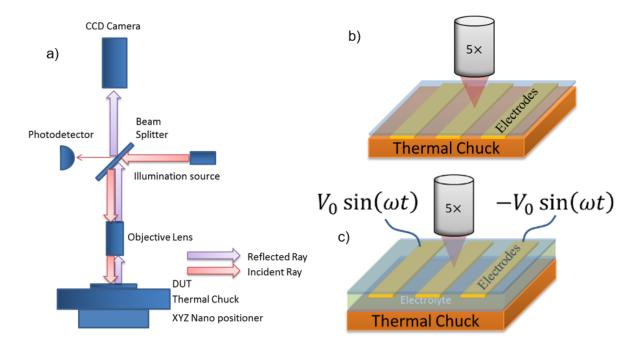

| 9.2  | a) Schematic of the thermal imaging measurement setup used for measuring the temperature rise at the electrodes. b) In calibration, the electrodes are heated using a thermal chuck. c) In activation, the electrodes are self-heated in the presence of applied voltage via Joule heating effect 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

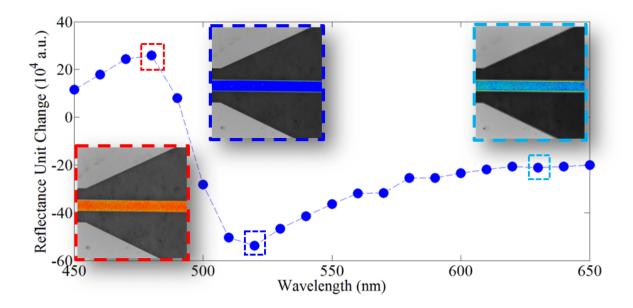

| 9.3  | Wavelength scan showing the thermore<br>flectance response ( $\Delta R/R$ ) at different illumination wavelengths. Only the middle electrode is electrically activated using a constant current source and shows a positive reflectance change response for<br>$\lambda$ >490 nm, a negative response for<br>$\lambda$ >490 nm, and an optimal response at $\lambda$ =520 nm. A 530 nm LED is<br>used for higher intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

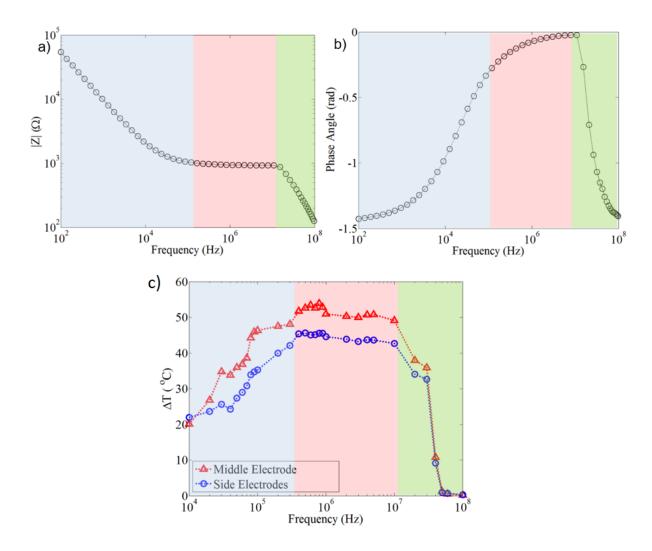

| 9.4 | a) Impedance magnitude and b) phase angle of 1.4 $S/m$ PBS solution in 400 $\mu$ m micro-fluidic channel from 100 Hz to 100 MHz c) Experimental temperature rise at the electrode/electrolyte interface with electrode excitation at 20 $V_{pp}$ and frequencies varying from 10 kHz to 100 MHz. Maximum temperature rise at these conditions is obtained at 51.5 °C $\pm$ 5.5 °C (standard deviations were constant for all data points)                                                                                                                                                                             | 178 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

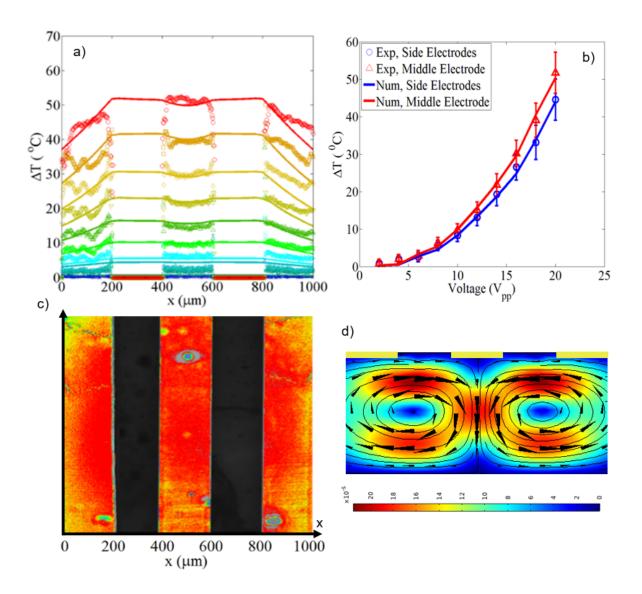

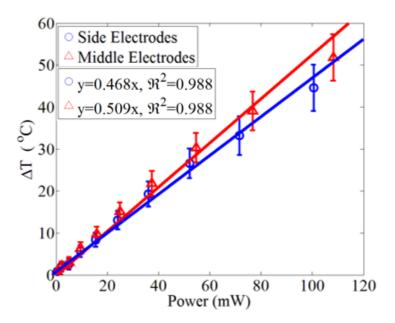

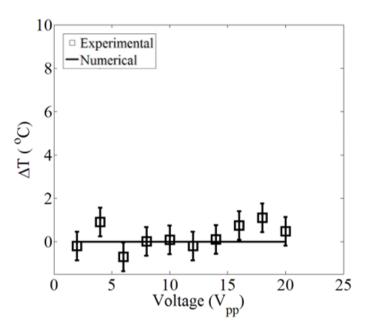

| 9.5 | Comparison of experimental (symbols) and numerical (solid lines) temperature fields on the electrode regions a) for different applied voltages at 5MHz. b) Experimentally and numerically obtained average temperature rise on the side and middle electrodes as a function of the applied peak to peak voltage. c) Measured temperature field on chromiumgold surface at 20 $V_{pp}$ (Top view). d) Flow field below the electrodes (represented with yellow) bars is shown with streamlines and the velocity magnitude contours given in terms of $\mu$ m/s. The simulation is performed at 5 MHz and 20 $V_{pp}$ . | 180 |

| 9.6 | Temperature rise at the electrode/electrolyte interface as a function of the dissipated power when the side electrodes are excited at 5 MHz and with different voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                              | 182 |